Electrically-erasable programmable read-only memory

La mémoire EEPROM (Electrically-Erasable Programmable Read-Only Memory ou mémoire morte effaçable électriquement et programmable) (aussi appelée E2PROM ou E²PROM) est un type de mémoire morte. Une mémoire morte est une mémoire utilisée pour enregistrer des informations qui ne doivent pas être perdues lorsque l'appareil qui les contient n'est plus alimenté en électricité.

Fonctionnement[modifier | modifier le code]

Le contenu de la mémoire EEPROM peut être facilement effacé et réécrit à l'aide d'un courant électrique.

Par exemple, quatre registres sont utilisés pour l'accès à la mémoire EEPROM d'un microcontrôleur PIC :

- EEDATA contient la donnée.

- EEADR contient l'adresse.

- EECON1 (Figure ci-dessous) est le registre de contrôle de l'accès à l’EEPROM. Cinq bits permettent cet accès :

- RD et WR initialisent la lecture ou l'écriture. Ils sont mis à 1 par le programme pour initier l'accès et mis à zéro par le système à la fin de l'accès.

- WREN autorise (1) ou non (0) l'accès en écriture.

- WRERR est mis à 1 par le système quand une opération d'écriture est interrompue par MCLR, reset ou le chien de garde.

- EEIF est un drapeau d'interruption signalant la fin de l'écriture physique dans la mémoire EEPROM. Il doit être mis à 0 par le programme.

- EECON2 joue un rôle spécifique lors de l'écriture.

PROM versus EEPROM[modifier | modifier le code]

À la différence d'une mémoire PROM qui ne peut être programmée qu'une seule fois, une mémoire EEPROM peut être effacée et reprogrammée plusieurs fois (de 100 000 à 1 000 000 fois) et peut être lue un nombre illimité de fois.

EPROM versus EEPROM[modifier | modifier le code]

Alors qu'il faut la retirer de l'appareil et la soumettre à un rayonnement ultra-violet pour effacer la mémoire EPROM (aussi appelée UVEPROM), la mémoire EEPROM peut être effacée par un simple courant électrique sans qu'il soit nécessaire de la retirer de l'appareil qui la contient.

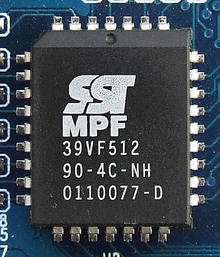

Les mémoires Flash[modifier | modifier le code]

Les mémoires Flash sont une variété de mémoire EEPROM rapide et effaçable par secteur complet, et non par case individuelle. On trouve plusieurs interfaces pour les adresser, série (24cxx) commandées par bus I2C, SPI… ou parallèles (29cxx), en 8/16/32 bits. C'est ce type de mémoire qui est utilisé dans les BIOS des cartes mères et dans des cartes électroniques où elles enregistrent des informations inhérentes à la carte comme l'adresse MAC, le nom du constructeur ou le type de produit. Elles servent également dans les cartes mémoires SD et CompactFlash, clés USB mais aussi dans les disques SSD.