Porte logique

Une porte logique (gate) est un circuit électronique réalisant des opérations logiques (booléennes) sur une séquence de bits. Cette séquence est donnée par un signal d'entrée modulé en créneau (signal carré), et cadencé de façon précise par un circuit d'horloge[1], ou quartz. Les opérations logiques sont réalisées électriquement par une combinaison de bascules ou inverseurs, à base de transistors[2],[3]. Étant donné les capacités d'intégration en électronique, un circuit intégré comporte généralement plusieurs portes à la fois[4].

Désignation[modifier | modifier le code]

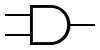

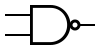

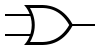

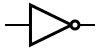

Une porte logique est désignée par l'opération logique qu'elle accomplit à partir des signaux d'entrée du circuit. La négation logique est représentée par un triangle (symbole du transistor selon la convention américaine ANSI), puisqu'elle est réalisée par un simple transistor, monté en inverseur[5]. On constate d'ailleurs que cette porte n'a qu'une seule entrée.

| Désignation | Fonction logique | Symbole ANSI | Table de vérité | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| NOT | inverseur |

|

| |||||||||||||||

| AND | et logique |

| ||||||||||||||||

| NAND | négation du "et logique" |

| ||||||||||||||||

| OR | ou inclusif |

| ||||||||||||||||

| NOR | négation du "ou inclusif" |

| ||||||||||||||||

| XOR | ou exclusif |

|

| |||||||||||||||

| XNOR | non ou exclusif |

|

|

Utilisation[modifier | modifier le code]

Les portes logiques sont constitutives des technologies numériques (par opposition aux technologies analogiques) : elles sont omniprésentes dans les ordinateurs, les filtres numériques, horloges et chronomètres numériques. Elles assurent une multitude de fonctions : unité arithmétique et logique, adressage et lecture de circuits de mémoire, conversion analogique-numérique et numérique-analogique, conversion DCB, décodage de codes Gray, etc.

Compteur[modifier | modifier le code]

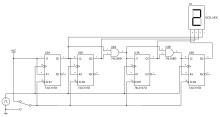

Le circuit ci-contre est alimenté en courant par le générateur à courant continu en haut à gauche, cependant que la base de temps est donnée par le signal d'horloge (le générateur de créneaux en bas à gauche). Les circuits 74LS107D sont de simples inverseurs à base de diode Schottky : ils détectent chaque changement d'état (de 0 à 1, ou de 1 à 0) de leur entrée, et envoient un signal 1 chaque fois qu'un changement a lieu (fonction de trigger).

Le principe de l'afficheur numérique DCD_HEX en haut à droite est simple[6] : en fonction du mot binaire codé sur quatre bits qu'il reçoit en entrée, il affiche la valeur décimale du nombre correspondant (p. ex. 0110 = 0x2³+2x2²+2x2+0x2⁰ = 6) en allumant les segments d'un afficheur sept segments.

Pour comprendre le fonctionnement du circuit ci-contre, il faut supposer les entrées initialement à 0 et cheminer de la gauche vers la droite du diagramme ; chaque émission d'un créneau par le générateur, produit une alternance de 0 à 1, puis de 1 à 0 qui déclenche un signal des circuits inverseurs ; avec les tables de vérité des portes du circuit, on peut ainsi déterminer l'état (0 ou 1) des quatre bits d'entrée du circuit afficheur le long de 4 créneaux émis en séquence.

Comparateur[modifier | modifier le code]

Le circuit comparateur ci-contre n'est guère plus difficile à comprendre : il suffit de construire la table de vérité des quatre sorties proposées en fonction des valeurs d'entrée (0 ou 1) de A et de B. La notation != signifie .

Unité arithmétique et logique[modifier | modifier le code]

Ce circuit (UAL en abrégé) permet de réaliser les opérations arithmétiques en base 2. Il prend en entrée deux mots de 2 bits (les opérandes) : soit par exemple A et B. Le bit des unités (LSB) est noté A[0] pour A, et B[0] pour B ; l'autre bit (MSB) est codé A[1] (resp. B[1]).

Les entrées A et B sont envoyés sur les quatre portes logiques à gauche du diagramme : de haut en bas, on reconnaît les portes XOR, AND, OR et XOR. Cette dernière porte forme l'étage d'entrée d'un circuit additionneur.

Outre les entrées A et B, le circuit tient compte d'une éventuelle retenue résultant d'une opération précédente (CARRY IN). De même, si le circuit réalise une opération aboutissant à un débordement, il émet un bit de retenue en sortie (CARRY OUT). Dans la pile d'un microprocesseur, ces bits spéciaux sont stockés dans un registre d'état[7].

Chaque bit est finalement séquencé par un multiplexeur (les deux blocs rectangulaires à droite du diagramme) pour former le résultat. La nature de la fonction à réaliser est donnée par le signal OP (codé sur 3 bits par une unité de contrôle) :

OP = 000 → XOR OP = 001 → AND OP = 010 → OR OP = 011 → Addition

Il reste quatre entrées inutilisées dans le multiplexeur : on pourrait s'en servir pour coder d'autres fonctions (soustraction, multiplication, division, inversion de A, inversion de B, etc.). De même, le bit OP[2] est apparemment inutile dans le cas de ce circuit ; mais il serait nécessaire pour coder davantage d'opérations que les quatre indiquées.

Réalisation[modifier | modifier le code]

Les premières portes logiques (fin des années 1950) étaient réalisées en technologie DTL. Au début des années 1960, elles ont été réalisées par des circuits intégrés TTL, à base de transistors bipolaires saturés. Cette technologie donnait des circuits miniaturisés, et elle a perduré jusqu'à la fin des années 1970 en raison de sa robustesse (elle offrait le durcissement requis pour les systèmes embarqués et applications militaires) et de sa relative insensibilité à l'électricité statique ; néanmoins, les circuits intégrés à transistor à effet de champ (p. ex. familles NMOS, PMOS, CMOS, HCMOS), quoique demandant davantage de précautions au câblage, réalisaient un niveau d'intégration encore bien supérieur aux TTL, et étaient plus économes en électricité : ils se sont imposés dès la fin des années 1960, en particulier pour les ordinateurs et leurs périphériques intelligents.

Notes[modifier | modifier le code]

- Pascal Mayeux, De la diode au microcontrôleur, vol. 1, Books on Demand, (ISBN 9782322459629), « 6. Les horloges », p. 193

- J.-C. Reghinot et J.-C. Pianezzi, Cours pratique d'électronique, Editions Radio, (ISBN 2709107988)

- R. Damaye, Circuits de logique, Éditions Radio, (EAN 2000189448554).

- Robert Keyes, « L'irremplaçable transistor », Pour la science, no 387, (lire en ligne).

- Reghinot et Pianezzi 1979, chap. « Circuit intégrés analogiques : l'amplificateur inverseur », p. 220.

- Reghinot et Pianezzi 1979, chap. « Eléments de calcul digital : décodage BCD 7 segments », p. 320.

- R. Zaks, La programmation du 6502, Sybex, , « 2. Organisation matérielle du 6502 : Les registres du 6502 »