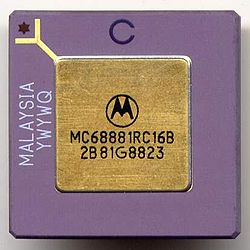

Motorola 68881

Apparence

(Redirigé depuis Motorola 68882)

Le Motorola 68881 est un coprocesseur mathématique destiné à travailler en complément à la famille de microprocesseurs m68k de Motorola.

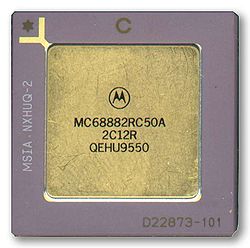

Le Motorola 68882 est une version améliorée du 68881, mais tout à fait compatible pour le reste.

Utilisation

[modifier | modifier le code]Les 68881 et 68882 ont été utilisés comme coprocesseurs optionnels dans beaucoup de modèles d'Atari, d'Amiga, de Macintosh.

Formats de nombre

[modifier | modifier le code]

Le Motorola 68881 connaît quatre formats de nombre :

| 95 | signe |

| 94-80 | exposant |

| 79-64 | toujours à zéro |

| 63-0 | mantisse |

| 63 | signe |

| 62-52 | exposant |

| 51-0 | mantisse |

| 31 | signe |

| 30-23 | exposant |

| 22-0 | mantisse |

| 95 | signe de la mantisse |

| 94 | signe de l'exposant |

| 93-92 | 00, ou NAN ou infini si 11 |

| 91-80 | les trois chiffres décimaux les moins significatifs de l'exposant |

| 79-76 | le chiffre décimal le plus significatif de l'exposant mantisse |

| 75-68 | pas tenu en compte |

| 67-64 | le chiffre le plus significatif de la mantisse |

| 63-0 | mantisse |

Registres de données et de contrôle

[modifier | modifier le code]Ses 8 registres de données (de FP0 à FP7) ont une largeur de 10 octets (80 bits), bien que la taille d'un réel de précision étendue puisse s'étendre sur 12 octets.

Il possède en outre 3 registres de contrôle :

| 3-0 | ? | zéro |

| 5-4 | ROUND | méthode d'arrondissement |

| 00 : au plus proche | ||

| 01 : zéro | ||

| 10 : moins l'infini | ||

| 11 : plus l'infini | ||

| 7-6 | PREC | précision de l'arrondissement |

| 00 : étendu | ||

| 01 : simple | ||

| 10 : double | ||

| 11 : réservé | ||

| 8 | INEX1 | sortie décimale inexacte |

| 9 | INEX2 | opération inexacte |

| 10 | DZ | division par zéro |

| 11 | UNFL | underflow |

| 12 | OVFL | overflow |

| 13 | OPERR | erreur d'opérande |

| 14 | SNAN | signal Not-A-Number |

| 15 | BSUN | Branch/Set in UNorderd |

| 7-0 | exception accrue |

| 2-0 | toujours à zéro |

| 3 | INEX!INEX2!OVFL |

| 4 | DZ |

| 5 | UNFL & INEX2 |

| 6 | OVFL |

| 7 | BSUN!SNAN!OPERR |

| 15-8 | statut des exceptions |

| 8 | INEX1 : sortie décimale inexacte |

| 9 | INEX2 : opération inexacte |

| 10 | DZ : division par zéro |

| 11 | UNFL : underflow |

| 12 | OVFL : overflow |

| 13 | OPERR : erreur d'opérande |

| 14 | SNAN : signal Not-A-Number |

| 15 | BSUN : Branch/Set in UNorderd |

| 23 | signe d'un quotient |

| 22-17 | quotient |

| 24 | NAN : Not A Number |

| 25 | I : infini |

| 26 | Z : zéro |

| 27 | N : négatif |

| 31-28 | zéro |

FPIAR (Floating Point Instruction Address Register) est le registre d'adresse de l'instruction en cours.

Puissance

[modifier | modifier le code]68881

[modifier | modifier le code]- 155000 transistors

- La version 16 MHz procure 160 KFLOPS

- La version 20 MHz procure 192 KFLOPS

- La version 25 MHz procure 240 KFLOPS

68882

[modifier | modifier le code]- 176000 transistors

- La version 25 MHz procure 360 KFLOPS

- La version 33 MHz procure 475 KFLOPS

- La version 40 MHz procure 576 KFLOPS

- La version 50 MHz procure 720 KFLOPS