Architecture de processeur

Une architecture externe de processeur[1],[2] ou architecture de jeu d'instructions[3] (ISA, de l'anglais instruction set architecture), ou tout simplement architecture (de processeur)[4],[5],[6], est la spécification fonctionnelle d'un processeur, du point de vue du programmeur en langage machine. L'architecture comprend notamment la donnée d'un jeu d'instructions, d'un ensemble de registres visibles par le programmeur, d'une organisation de la mémoire et des entrées sorties, des modalités d'un éventuel support multiprocesseur, etc.

Le terme externe employé ici permet de bien faire la différence avec la microarchitecture ou architecture interne, qui s'intéresse à l'implémentation pratique du comportement spécifié par une architecture externe. Une architecture externe donnée peut être implémentée sous forme de plusieurs microarchitectures.

Définitions[modifier | modifier le code]

Une architecture externe de processeur est le modèle du processeur vu de l'extérieur, c'est-à-dire par le programmeur en langage machine, le compilateur ou le noyau du système d'exploitation. Il s'agit de l'interface entre le matériel et le logiciel.

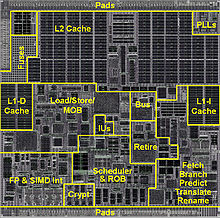

Cette interface peut être implémentée dans divers processeurs. L'organisation pratique de ces derniers est appelée microarchitecture ou architecture interne[1]. Par opposition à l'architecture qui correspond au modèle de la machine vu par le programmeur, les spécificités d'une microarchitecture sont invisibles pour ce dernier. Par exemple, la microarchitecture peut spécifier l'existence de mémoires cache, de renommage de registres, de pipelines, de prédiction de branchement, etc. Une microarchitecture peut ensuite donner lieu à une ou plusieurs réalisations matérielles.

Pour résumer, Andrew Tanenbaum[7] distingue trois niveaux matériels dans un ordinateur :

- niveau no 2 — architecture externe ou de jeu d'instructions (ISA) ;

- niveau no 1 — microarchitecture ou architecture interne ;

- niveau no 0 — réalisation en logique numérique.

Exemple (fictif) :

- niveau architecture externe : il existe huit registres d'usage général. L'instruction ADD effectue une addition entre deux quelconques de ces registres et met le résultat dans un quelconque troisième ;

- niveau microarchitecture (architecture interne) : le traitement des instructions est pipeliné[8] et deux unités arithmétiques et logiques sont capables d'effectuer l'addition de l'instruction ADD ;

- niveau réalisation : le processeur est réalisé dans une technologie CMOS avec trois niveaux de métal et une finesse de gravure de 130 nanomètres.

Pour une architecture donnée, on peut avoir plusieurs microarchitectures, et une microarchitecture donnée peut servir de base à plusieurs réalisations. Par exemple l'architecture System 360 d'IBM a été disponible dès le départ en cinq microarchitectures différentes ayant naturellement des performances et un coût différent (c'est d'ailleurs dans le contexte de la définition de cette architecture que la nomenclature ci-dessus a été raffinée[4]). Chez Intel, l'architecture IA-32, implémentée pour la première fois dans le 80386, possède des implémentations ultérieures très différentes : par exemple, le Pentium a introduit une microarchitecture pipelinée de type superscalaire avec prédiction de branchement. En outre, l'architecture IA-32 a été implémentée par d'autres fondeurs, en particulier AMD.

Naturellement les interactions entre les trois niveaux sont complexes. Les contraintes de réalisation limitent les choix micro-architecturaux et le désir de pouvoir choisir une microarchitecture donnée influence la définition de l'architecture. Si les avantages de la compatibilité forcent à vouloir garder l'architecture constante, vouloir avoir une microarchitecture et une réalisation efficace pousse vers une évolution, soit par extension compatible (ajout d'instructions par exemple), soit en précisant des zones floues ou même en invalidant ce qui autrefois était autorisé.

Éléments d'une architecture externe[modifier | modifier le code]

Dans la plupart des architectures, les programmes manipulent des registres de travail. Ces derniers sont donc à la base de l'architecture. Cependant, le processeur peut comporter d'autres registres, internes, non visibles du programmeur : ceux-ci ne font pas partie de l'architecture.

L'accès aux données de la mémoire se fait selon un certain nombre de modes d'adressage qui sont spécifiés au niveau de l'architecture. De plus, cette dernière définit la vue logique qu'ont les programmes de la mémoire, et la façon dont est réalisée la liaison avec la mémoire physique. De même on spécifie les modalités d'accès aux entrées-sorties : registres spécialisés (c'est souvent le cas dans les microcontrôleurs), espace mémoire particulier (auquel cas les modes d'adressage sont souvent plus réduits que dans les espaces mémoire normaux), adresses particulières dans l'espace mémoire normal. Les types de données manipulés par le processeur doivent être précisés.

Les registres, la mémoire et les entrées-sorties sont manipulées par les instructions machine des programmes. Le jeu d'instructions est donc une donnée conséquente de l'architecture : il spécifie très précisément le comportement de chaque instruction-machine.

Une architecture définit la façon dont sont gérées les erreurs ou exceptions.

Dans le cas d'une architecture qui supporte le multiprocesseur, la façon dont les différents processeurs communiquent et se synchronisent doit être spécifiée.

Idéalement, on peut penser que les divers caches que peut intégrer un processeur (mémoire cache, TLB, etc.) pourraient être transparents pour le programmeur, donc hors du champ de l'architecture externe. Cependant, il est le plus souvent nécessaire que les programmes (en général le système d'exploitation) interagissent avec les caches (par exemple, pour invalider des entrées du TLB lorsque nécessaire). L'architecture externe décrit alors le rôle et l'interface de ces caches.

Classification des architectures[modifier | modifier le code]

Architecture CISC[modifier | modifier le code]

Une architecture CISC propose de nombreux modes d'adressage, dont certains sont souvent complexes. Le jeu d'instructions comporte souvent de nombreuses instructions complexes qui seront réalisées en plusieurs cycles.

Exemples : x86 étendue en IA-32, elle-même étendue en x64 ; Motorola 680x0.

Architecture RISC[modifier | modifier le code]

Une architecture RISC propose un jeu d'instructions relativement réduit. Chacune de ces instructions est censée être exécutée en un seul cycle. Les modes d'adressage sont plus simples que dans une architecture CISC. L'architecture propose en général un nombre important de registres généraux. Ces caractéristiques favorisent une utilisation optimale du pipeline au niveau de la microarchitecture.

Exemples : SPARC, POWER, PowerPC, MIPS et ARM.

Architecture VLIW[modifier | modifier le code]

Ce concept fait reposer une partie de la gestion du pipeline sur le compilateur : le processeur reçoit des instructions longues qui regroupent plusieurs instructions relativement plus simples.

Architecture vectorielle[modifier | modifier le code]

Alors que les instructions des processeurs traditionnels traitent un nombre (un scalaire) à la fois, les instructions des processeurs vectoriels peuvent travailler sur des vecteurs.

Exemples : les machines Cray.

Architectures dataflow[modifier | modifier le code]

Jeux d'instructions supplémentaires SIMD[modifier | modifier le code]

Afin d'améliorer les performances en calcul vectoriel (lié à l'algèbre linéaire) des processeurs traditionnels, on peut adjoindre à leur architecture de base une unité dédiée aux traitements SIMD, effectuant des calculs sur plusieurs données en une seule instruction On compte notamment les technologies suivantes :

- dans le monde PowerPC : AltiVec ;

- dans le monde ARM : NEON ;

- dans le monde x86 : MMX (multimedia extensions), SSE (streaming SIMD extensions), AVX (advanced vector extensions).

Ce type d'unité de calcul a été une version économique des processeurs vectoriels utilisé sur des supercalculateurs tels que les Cray. Cette économie était pertinente dans les années 1990, cependant on voit réapparaître, dans l'Architecture RISC-V par exemple, des processeurs vectoriels. Dans un processeur vectoriel, on fournit à l'unité de calcul des instructions à effectuer sur les données, et une table de données à parcourir avec ces instructions, elles sont ensuite effectuée de façon linéaire.

Notes et références[modifier | modifier le code]

- Les termes d'architectures interne et externe ont notamment été repris en 1998 dans le document « Principes d'architecture externe des ordinateurs »(Archive.org • Wikiwix • Archive.is • Google • Que faire ?) de « François Anceau »(Archive.org • Wikiwix • Archive.is • Google • Que faire ?), titulaire de la Chaire des techniques fondamentales de l'informatique au CNAM.

- F. Anceau, The Architecture of Microprocessors, Addison-Wesley, 1985, « For any computer, there are two distinct architectures : (a) the external architecture which describes the machine as seen by its users (programmers) in terms of its instruction set [and] its facilities (number of registers, etc.), (b) the internal architecture which describes how the machine is physically organized [...]. »

- Par exemple dans Nicholas P. Carter, Architecture de l'ordinateur, Schaum's, 2002 ou Architecture de l'ordinateur : Cours et exercices, Andrew Tanenbaum, Jean-Alain Hernandez (trad.), René Joly (trad.), Dunod, 2001.

- G. M. Amdahl, G. A. Blaauw et F. P. Brooks, Jr., « Architecture of the IBM System/360 », IBM Journal of Research and Development, volume 8, numéro 2, p. 87-101, 1964. Voir notamment la note suivante : « The term architecture is used here to describe the attributes of a system as seen by the programmer, i.e., the conceptual structure and functimal behavior, as distinct from the organization of the data flow and controls, the logical design, and the physical implementation. »

- B. Shriver et B. Smith, The Anatomy of a High-Performance Microprocessor : a Systems Perspective. The IEEE Computer Society, 1998, p. xi : « Architecture refers to the instruction set, resources, and features of a processor that are visible to software programs running on the processor. The architecture determines what software the processor can directly execute and essentially forms a specification for the microarchitecture. The term architecture as defined here is often called the instruction set architecture. »

- D.A. Patterson, J.L. Hennessy, Computer Organization & Design, Elsevier, 2005, p. 21 : « One of the most important example of abstraction is the interface between hardware and lowest-level software. Because of its importance, it is given a special name: the instruction set architecture, or simply architecture, of a machine. »

- Architecture de l'ordinateur : Cours et exercices, Andrew Tanenbaum, Jean-Alain Hernandez (trad.), René Joly (trad.), Dunod, 2001.

- Mise à la file dans le pipeline.

Bibliographie[modifier | modifier le code]

- Architecture de l'ordinateur, Andrew Tanenbaum

- Computer Architecture, G.A. Blaauw et F.P. Brooks Jr, Addison Wesley.

- Computer Architecture, A Quantitative Approach, J.L. Hennesy et D.A. Patterson, Morgan Kaufmann

- Microprocessors, a programmer's view, R.B.K. Dewar et M. Smosna, McGraw-Hill